- Qualifi Level 7 Diploma Unit EDML710 Contemporary Issues in Education (K/650/6690) Assignment Brief 2026

- Qualifi Level 7 Diploma Unit EDML709 Triangulating Theory and Practice in an Educational Context (F/650/6689) Assignment Brief 2026

- Qualifi Level 7 Diploma Unit EDML708 Research Methods for Childhood, Education and Family Support (D/650/6688) Assignment Brief 2026

- Qualifi Level 7 Diploma Unit EDML707 Postgraduate Study of Childhood, Education and Family Support (A/650/6687) Assignment Brief 2026

- IMA7001 International Marketing Management Assessment 1 Brief 2026 | RCL

- Qualifi Level 7 Diploma Unit EDML706 Research Methods in Education (F/618/3140) Assignment Brief 2026

- Qualifi Level 7 Diploma Unit EDML705 Leading Reflective Practice in Education (L/618/3139) Assignment Brief 2026

- Qualifi Level 7 Diploma Unit EDML704 Pedagogy and Practice in Education (J/618/3138) Assignment Brief 2026

- Qualifi Level 7 Diploma Unit EDML703 Managing Change in an Education Context (F/618/3137) Assignment Brief 2026

- Qualifi Level 7 Diploma Unit EDML702 Contemporary Issues in Education: Theory, Policy and Practice (A/618/3136) Assignment Brief 2026

- Qualifi Level 7 Diploma Unit EDML701 Leadership Qualities and Practice in Education (T/618/3135) Assignment Brief 2026

- Qualifi Level 7 Diploma Unit CPD703 Effective Communication through CPD (K/617/7493) Assignment Brief

- Qualifi Level 7 Unit CPD701 Contemporary Issues Underpinning Leadership in CPD (D/617/7491) Assignment Brief 2026

- Qualifi Level 7 Diploma Unit CPD702 Developing Research and CPD (H/617/7492) Assignment Brief

- QUALIFI Level 6 Diploma Unit 1 Principles of Teaching and Learning Theory and Practice (Y/618/5461) Assignment Brief 2026

- HCR7013 Contemporary Challenges in Public Health Assessment Brief 2026 | Arden University

- BTEC HND Unit 41 Database Management Systems Assignment Brief 2026

- MKT744 / MKT77216 Global Marketing and Sales Development Assignment Brief 2026 | Ulster University

- NURS 1584 Introduction to Preparation for Professional Practice Assessment Brief 2026 | UOG

- SH4011 Research and Academic Practice Assessment brief 2026 | LMU

BÿL2006 Computer Architecture Project PART 2 –Eneral Design Of The Project: Control Unit Design: Mib Design, Assignment , UOC, UK

| University | University Of Cambridge (UOC) |

| Subject | BÿL2006 Computer Architecture Project PART 2 |

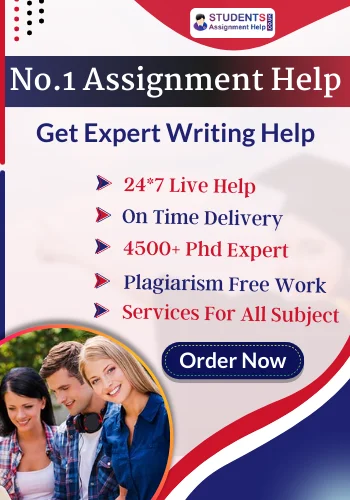

GENERAL DESIGN OF THE PROJECT:

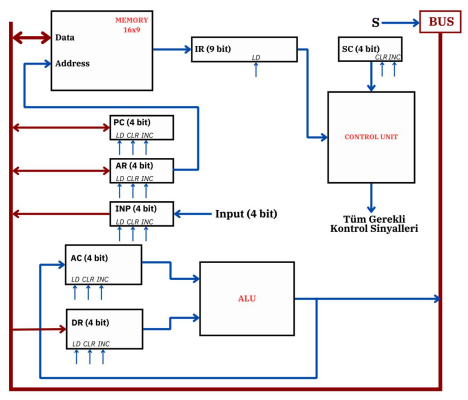

CONTROL UNIT DESIGN:

BÿL2006 COMPUTER ARCHITECTURE PROJECT PART 2 – MIB DESIGN

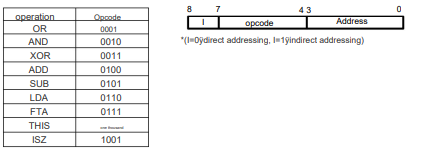

1. Memory-Reference Instructions:

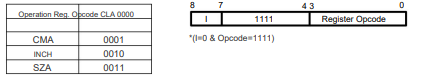

2. Register reference instructions:

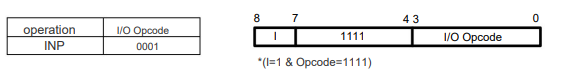

3. I/O Reference Instructions:

Buy Answer of This Assessment & Raise Your Grades

Project Expectations

1. The processor unit you designed will perform all operations in the Operation column given in the tables. must be capable of being fulfilled separately.

2. The designs of AC, DR, PC, IR, INP, SC, AR registers should be made in detail. This registers must be in the number of bits shown in the figure.

3. All data buses must be designed for 4 (four) bit data transfer.

4. Carry out output (belonging to the ALU) must be calculated.

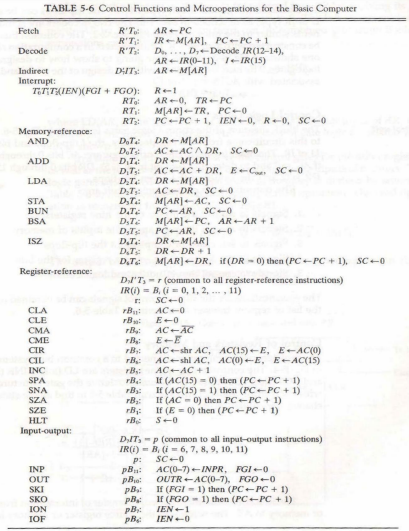

5. Create your own table similar to the table given in Table 5.6 (ANNEX-1). is required.

6. Control Unit structure must be designed logically.

7. There should be two clock inputs in the designed system. Memory and Registers are clocked differently. It must have inputs (Mem_clock=4xReg_clock)

8. Waveform outputs (University Program Vector Waveform File) should be shown.

9. The developed system performs all the above-mentioned operations without any errors. is expected.

ANNEX-1: MANO TABLE 5.6

Are You Looking for Answer of This Assignment or Essay

Seeking assistance with your BÿL2006 Computer Architecture Project? Look no further! Our assignment help online service offers expert Computer Architecture Assignment Help by PhD Experts. Need assistance with General Design Of The Project, including Control Unit Design and Mib Design? Let us do my assignment for me online. UK students can trust our support. Get in touch now for personalized assistance and excel in your assignments!