- Unit 560 Support Individuals with Multiple Conditions and/or Disabilities (T/601/5253) Assignment Brief 2026

- Unit 440 Advanced Communication Skills Assignment Brief 2026

- Unit 706 Promote Rights and Values in Assistive Technology in Social Care (D/506/8163) Assignment Brief 2026

- Unit 401 Support the Development of Community Partnerships (M/601/9494) Assignment Brief 2026

- COM4015 Introduction to Databases Assessment Brief 2026 | Arden University

- COM4014 Introduction to Web Authoring Assessment Brief 2026

- OTHM Level 4 Communication in Business (A/650/1103) Assignment Brief 2026

- Operations and Logistics Management (T/650/1101) Assignment Brief 2026

- OTHM Level 4 Finance and Accounting (Y/650/1102) Assignment Brief 2026

- Leading and Managing Teams (D/650/1104) Assignment Brief 2026

- Logistics and the Business Environment (R/650/1100) Assignment Brief 2026

- FDY3004 Advancing Your Academic Skills Assignment Brief 2026 | Arden University

- Unit 433 Manage Finance within own Area of Responsibility in Health and Social Care or Children and Young People’s Settings (T/506/6368) Assignment Brief 2026

- Unit 651 Appraise Staff Performance (J/504/2219) Assignment Brief 2026

- Unit 567 Share Knowledge and Good Practice (A/602/6237) Assignment Brief 2026

- Unit 435 Mentoring in Social Care (J/506/6052) Assignment Brief 2026

- Business Start-up: Conception to Market (M/650/1155) Assignment Brief 2026

- Management Accounting and Decision Making (L/650/1154) Assignment Brief 2026

- Business Law for Managers (K/650/1153) Assignment Brief 2026

- Marketing for Managers (J/650/1152) Assignment Brief 2026

CE869: Your task for this assignment is to implement a 16 bit CPU To make the assignment feasible within the time frame: High Level Logic Design Assignment, UOE, UK

| University | university of Essex (UOE) |

| Subject | CE869: High Level Logic Design |

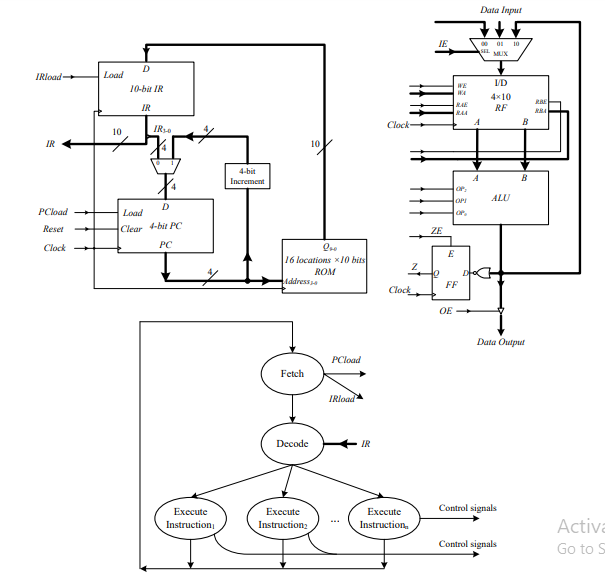

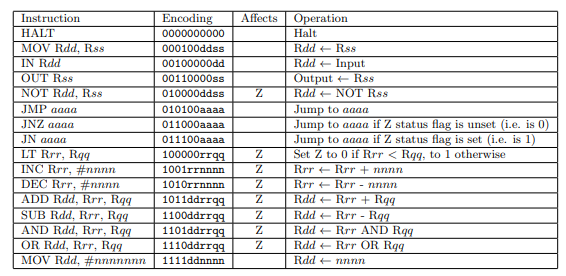

Your task for this assignment is to implement a 16 bit CPU. To make the assignment feasible within the time frame available for this module, the type of CPU will be fairly simple. In particular, the “program sequencing/control flow instruction” datapath can be modeled after the one on the left of Figure 1, while the “arithmetic/logic instruction” datapath can follow a structure like the one on the right in the same figure. Please notice that when RAE and/or RBE is low, the corresponding output(s) will simply match the input “I” to the register file. The opcodes for the instructions that the CPU is required to implement are given in Table 1. You are also required to implement a decode unit in the control unit to interpret the ‘Effects’ and control signals from the output of each instruction.

Figure 1: The figure shows the “program sequencing/control flow instruction” datapath and the “arithmetic/logic instruction” datapath (right).

To test your CPU, you will design the main entity that instantiates the CPU and connects it to the Basys3 peripherals. The sixteen switches of the Basys3 board will represent the input to the CPU while its output will be shown as a hexadecimal number in the four digits of the 7-segment display. The central button will be used as a reset signal to the CPU.

To test the CPU you will be asked to code two programs in the assembly and machine languages of the CPU, implementing the following tasks

- Given a nonzero number N as input, output the sum of the natural numbers less than N;

- Given a number N as input, output “N div 11” (i.e. the integer quotient of the division between N and 11, “TRUNC(N/11)”);

These design specifications should be interpreted as guidelines and should not constrain you from improving the CPU by doing modifications that you think would result in a better “product”. The test programs above, though, should be implemented using only the instructions in Table 1. You are welcome to implement more elaborated programs to test the capabilities and the limitations of the CPU.

Do You Need Assignment of This Question