- OTHM Level 7 Diploma Unit Supply Chain and Operations Management (R/616/2728) Assignment Brief 2026

- PSYM221Z Introduction to Statistics Summative Assessment 2, 2026 | University of Exeter

- SH4012QA Human Growth & Development Assessment Brief 2026 | LMU

- OTHM Level 7 Diploma Unit Strategic Marketing (Y/616/2732) Assignment Brief 2026

- OTHM Level 7 Diploma Unit Strategic Financial Management (L/616/2727) Assignment Brief 2026

- OTHM Level 7 Diploma Unit Advanced Business Research Methods (J/616/2726) Assignment Brief 2026

- OTHM Level 7 Diploma Unit Strategic Human Resource Management (F/616/2725) Assignment Brief 2026

- OTHM Level 7 Diploma Unit Strategic Leadership (R/617/5012) Assignment Brief 2026

- OTHM Level 7 Diploma Unit Strategic Management (A/616/2724) Assignment Brief 2026

- MIDP4100 Midwife as Scholar 1 Assessment Brief 2026 | University of Cumbria

- OTHM Level 7 Diploma Unit Entrepreneurship and Innovation ( Y/616/2729 ) Assignment Brief 2026

- ILM Level 3 Unit 303 Reflecting on Coaching Skills within an Organisational Context (M/617/2845) Assessment Brief 2026

- ILM Level 3 Unit 302 Undertaking an Extended Period of Coaching within an Organisational Context (H/617/2843) Assessment Brief 2026

- ILM Level 3 Unit 301 Undertaking Coaching within an Organisational Context (D/617/2842) Assessment Brief 2026

- ILM Level 3 Unit 300 Understanding Good Practice in Coaching within an Organisational Context (Y/617/2841) Assessment Brief 2026

- Qualifi Level 7 Diploma Unit EDML710 Contemporary Issues in Education (K/650/6690) Assignment Brief 2026

- Qualifi Level 7 Diploma Unit EDML709 Triangulating Theory and Practice in an Educational Context (F/650/6689) Assignment Brief 2026

- Qualifi Level 7 Diploma Unit EDML708 Research Methods for Childhood, Education and Family Support (D/650/6688) Assignment Brief 2026

- Qualifi Level 7 Diploma Unit EDML707 Postgraduate Study of Childhood, Education and Family Support (A/650/6687) Assignment Brief 2026

- IMA7001 International Marketing Management Assessment 1 Brief 2026 | RCL

CE869: Your task for this assignment is to implement a 16 bit CPU To make the assignment feasible within the time frame: High Level Logic Design Assignment, UOE, UK

| University | university of Essex (UOE) |

| Subject | CE869: High Level Logic Design |

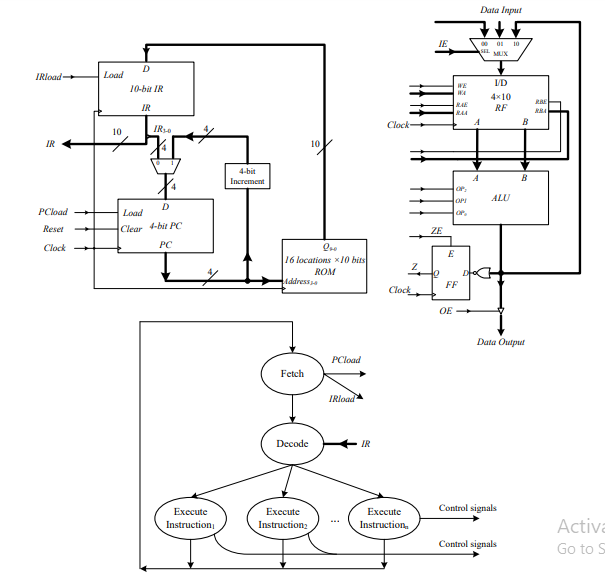

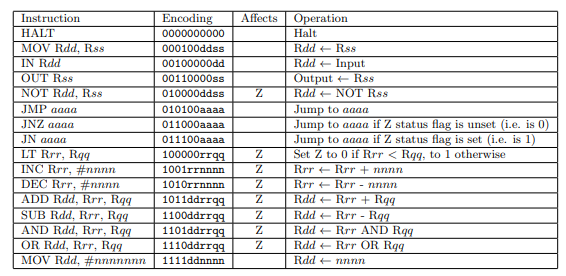

Your task for this assignment is to implement a 16 bit CPU. To make the assignment feasible within the time frame available for this module, the type of CPU will be fairly simple. In particular, the “program sequencing/control flow instruction” datapath can be modeled after the one on the left of Figure 1, while the “arithmetic/logic instruction” datapath can follow a structure like the one on the right in the same figure. Please notice that when RAE and/or RBE is low, the corresponding output(s) will simply match the input “I” to the register file. The opcodes for the instructions that the CPU is required to implement are given in Table 1. You are also required to implement a decode unit in the control unit to interpret the ‘Effects’ and control signals from the output of each instruction.

Figure 1: The figure shows the “program sequencing/control flow instruction” datapath and the “arithmetic/logic instruction” datapath (right).

To test your CPU, you will design the main entity that instantiates the CPU and connects it to the Basys3 peripherals. The sixteen switches of the Basys3 board will represent the input to the CPU while its output will be shown as a hexadecimal number in the four digits of the 7-segment display. The central button will be used as a reset signal to the CPU.

To test the CPU you will be asked to code two programs in the assembly and machine languages of the CPU, implementing the following tasks

- Given a nonzero number N as input, output the sum of the natural numbers less than N;

- Given a number N as input, output “N div 11” (i.e. the integer quotient of the division between N and 11, “TRUNC(N/11)”);

These design specifications should be interpreted as guidelines and should not constrain you from improving the CPU by doing modifications that you think would result in a better “product”. The test programs above, though, should be implemented using only the instructions in Table 1. You are welcome to implement more elaborated programs to test the capabilities and the limitations of the CPU.

Do You Need Assignment of This Question